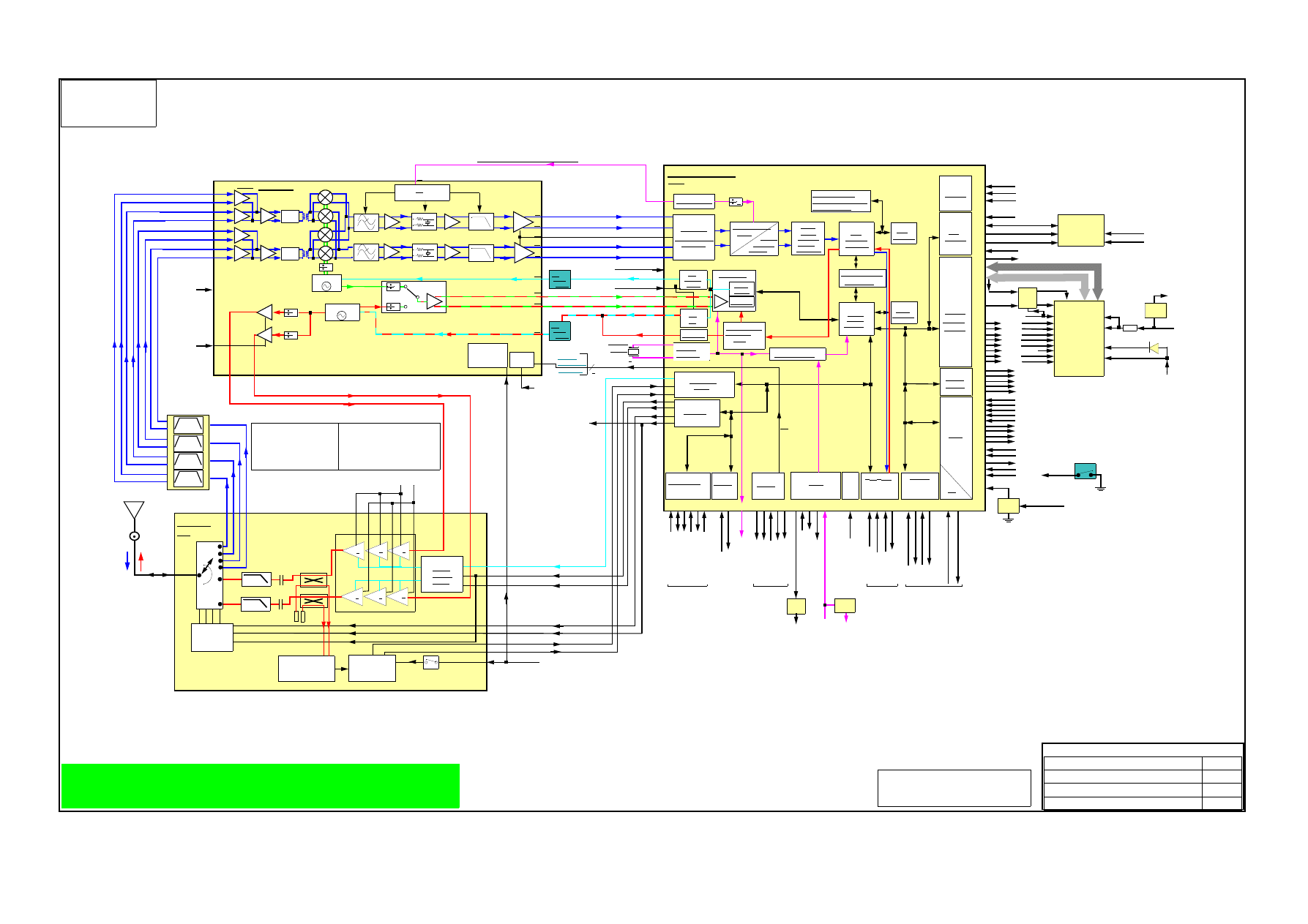

GSM SERVICE SUPPORT GROUP

2004.04.02

LEVEL 3 AL Block Diagram

Rev. 1.1

V30x, V400, V50x, V600

Michael Hansen, Alexander Buehler

Page 1of 2

Internal

Antenna

J1

AOC_DRIVE

Antenna

Switch

FL100

Quard Saw Filter

4

3

2

5

RX CP

TX CP

D5

47

Synth F/B

SYNTH FD P

SYNTH FB N

TX_IN_HB

TX_IN_LB

38

39

41

42

44

CM IN

25

C9

BB I

BB IX

BB Q

BB QX

A8

B8

A9

B9

27

28

29

30

B6

LP Filter

Tracking

Control

Tracking Osc.

RF_REG

RX

Charge

TX

CP

C4

D9

7, 8, 10, 11, 15, 18, 21, 37, 43, 48

NEP_IO_REG

RF_CS

RF_DATA

RF_CLK

3

U8, V7, W9

GMSK Mod &

Mod DAC

(TX)

PA Control

(PAC)

Y805

3

1

A4

Power Detector

PACII IC

VCC

2

39

6

17

LOWB_HIGH

T6

TX_EN

U6

8,16

Switch

Control

Circuit

W7

N9

RF 5V REG

EXC_EN

EURO_US

PA_REF

PA_DET

D12

B10

PA_REF

PA_DET

LOWB HIGH

TX_EN

EXC_EN

EURO_US

Digital Channal

Filters

26 MHz

Timer

19

18

14

15

13

Matching and

Combiner Network

LP

LP

Low Band

High Band

3

3

DMA

1Mbit RAM

PMA

AAF

2

2

1

1

Pump

Super Filter

Generator

2,45V

5

4

B4

A6

720 - 915 MHz

1710 - 1785 MHz

880 - 915 MHz

Synthesizer

Prescaler

Phase

Detect

Dual ADC

DSP

DSP

UltraLite

104 MHz

DSP Peripherals

accelerator, encryption

Timer, Interupts

Shared Memory

MCU

52 MHz

ARM7

MCU

26 MHz

Oscillator

B4

Memory

Memory

2

3

6

SIM

Interface

SIM DIO

SIM RST

SIM CLK

J4

L1

K3

SIM PD

1,5

VSIM

4

GND

R1

MQSPI

Display

Connector

J1350

SIM

GPIO

M1

1.8 or 3V

SIM Card

VSIM_EN

External

Interface

Memory

U13

(decoupling analog GND)

HP-Filter

D8

TX

Loop

Filter

Clock Generator

L1 Timer

NEPTUNE LTS

ALGAE

U150

U800

XTAL

EXTAL

Interface

UART / USB

Interface

TRK CLK

B5

35

( 26MHz for Digital IF Filter syncronisation)

EXC EN

EXC_EN

(Post Mixer Amplifier)

BB

Out

BB

Out

IF Amp.

2 Pole Filter

L & H

Band

V30x, V400, V50x, V600

L

o

w

B

a

n

d

8

5

0

M

H

z

EGSM: CH 37 -- 942,4Mhz

DCS: CH 700 -- 1842,8MHz

PCS: CH 661 -- 1960MHz

RX MID CHANNELS

GSM: CH 62 -- 947,4 MHz

850: CH190 -- 881,6

EGSM: 880 - 915MHz

DCS: 1710 - 1785MHz

TX VCO FRQ. RANGE

850: 824 - 850Mhz

PCS: 1850 - 1910MHz

EGSM: CH 37 - 897,4Mhz

DCS: CH 700 - 1747,8MHz

TX VCO MID CHANNELS

GSM: CH 62 - 902,4MHz

PCS: CH 661 - 1880 MHz

850: CH 190 - 836,6

GSM : 890 - 915 MHz

Direct

Memory

Access

Controller

Analog / Digital

Converter

SPI

32

33

34

31

36

2

4

TX VCO

3.4 - 3.7 GHz

100kHz

100kHz

N

and LO

Digital

If Mixer

BaseBand

Port Interface

Serial Audio

B

B

S

A

P

T

X

B

B

S

A

P

R

X

B

B

S

A

P

F

S

B

B

S

A

P

C

L

K

B13

B12

A12

D13

(f

ra

m

es

y

n

c)

(c

lo

ck

)

(tx)

(rx)

TX_MOD

A10

C

L

K

1

3

M

H

z

W13

C15

C16

D15

A16

Keypad

Interface

B

B

S

P

I

C

L

K

B

B

S

P

I

M

O

S

I

B

B

S

P

I

M

IS

O

P

C

A

P

C

S

Neptune PCap

Communication

MQSPI

T11

V12

V11

W12

S

T

A

N

D

B

Y

G8

U802

S

T

A

N

D

B

Y

Buffer

C

L

K

3

2

K

H

Z

E3

B14

P

C

A

P

I

N

T

R

E

S

E

T

B

V13

(1

3

M

H

z)

(W

a

tc

h

d

o

g

)

W

D

O

G

Mechanical

Antenna Switch

M3

(VCC)

R

F

_

R

E

G

(V

C

C

)

V6

RX_EN

O

W

B

W11

O

n

e

W

ir

e

d

at

a

fr

o

m

B

at

te

ry

V14

W8

OPT1

OPT2

T7

SW B+ EN

RX

Loop

Filter

POWER

SPI

VBUCK

NEP IO REG

(VCC + 2.775V)

(VCC + 1,875V)

AGC

RF Det.

AGC

RF Det.

RX VCO

3.6 - 3.9 GHz

n

LNA

LNA

LNA

LNA

2

3

2

7

2

9

Low Band

850MHz

Low Band

900MHz

High Band

1800MHz

High Band

1900MHz

21

6

1

and Matching

L

o

w

B

an

d

9

0

0

M

H

z

H

ig

h

B

an

d

1

8

0

0

M

H

z

14

15

12

13

8

9

10

11

H

ig

h

B

a

n

d

1

9

0

0

M

H

z

19

20

22

23

16

17

13

14

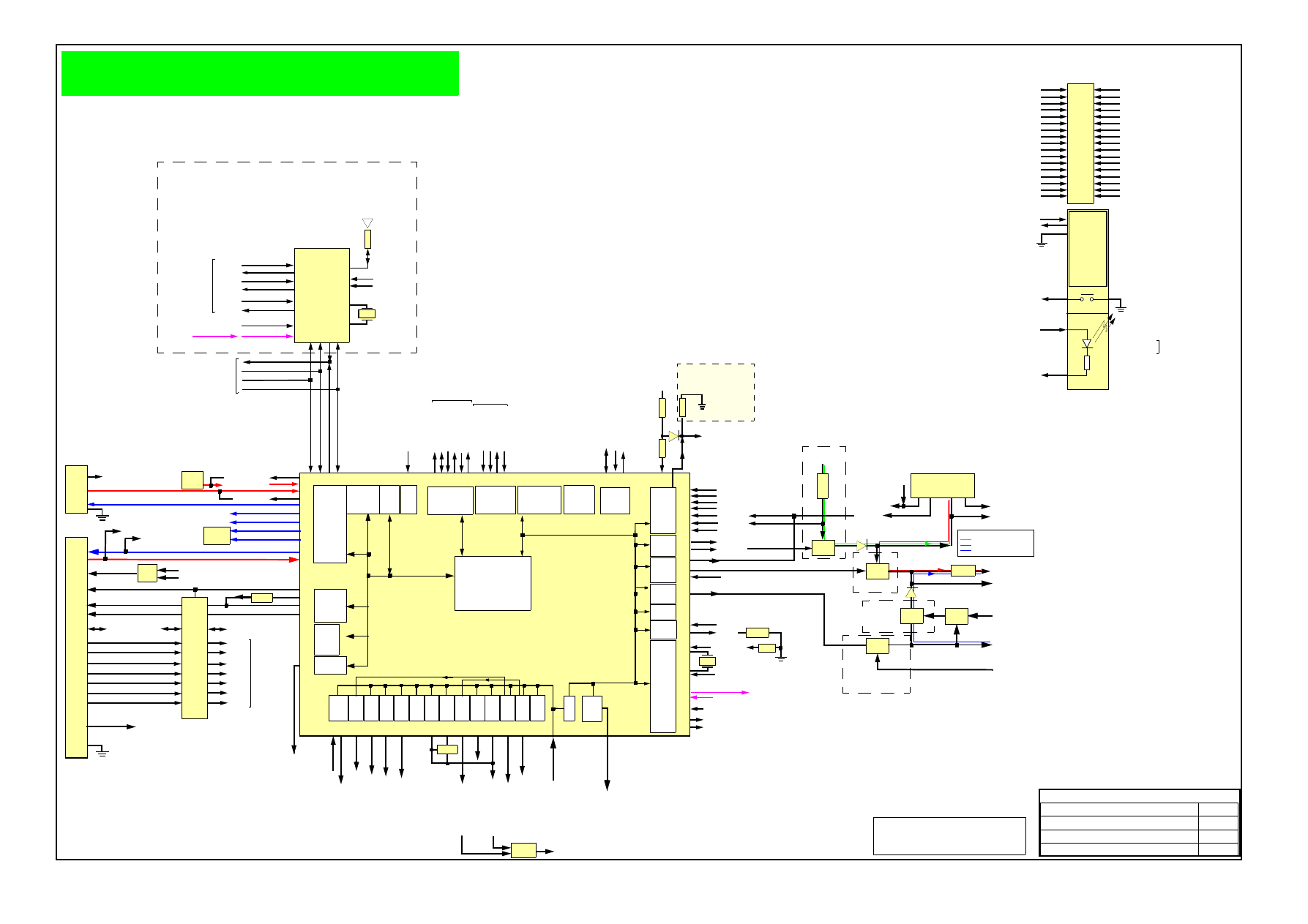

EAGLE

U50

CMOS

PA Bias

Circuit

33

32

10

34

11

12

PA_B+ PA_B+

(to Algae)

(VCC)

U700

VBUCK

EB1_B

EB0_B

OEB

R WB

CS1B

ADDRESS BUS

DATA BUS

K16

J19

G17

T16

BURSTCLK

LBAB

CS0B

ECBB

V17

T19

L16

W18

N18

A1-24

D0-15

32 MB Flash

RESET OUT

F3

C2

D6

E5

F5,D5

J2,H1,H8

G7

C6

B5,B6...

CE_2

CE_1

3 5

6

4

U701

PMODE

K8

F4

K1

G8

ADDR.24

1

R707

RST

U1301

Buffer

(t

o

J

1

3

0

0

)

(from PCAP -

BATT DETB

)

POWER CUTS VCC

(VCC +1,875V)

E2

U

S

B

V

P

IN

U

S

B

X

R

X

D

R

T

S

U

S

B

V

P

O

U

T

T

X

D

U

S

B

V

M

IN

R

X

D

U

S

B

T

X

E

N

B

U

S

B

S

E

0

B16

A17

RF REG

K2

VSIM

A11

N17

Neptune PCap

USB/ RS232

Communication

(f

ro

m

P

C

ap

)

R

E

S

E

T

O

U

T

W5

(t

o

U

7

0

0

)

C

L

K

3

2

K

H

Z

B

One

Bus

Wire

U1300

Inverter

RESET OUT B

RX EN

9

(from/ to Neptune

Serial Audio for Ringtone

and Voice Audio)

G12

MIDRATE2

LOGIC SENSE

T13

R

X

D

2

T

X

D

2

R

T

S

2

C

T

S

2

UART2

N17

N13

V16

D16

Universal

Asynchron.

Rx /Tx

(from/ to U301 BT,

Neptune - BT - Neptune

Communication and Wakeup)

BT

B

L

U

E

_

W

A

K

E

B

B

L

U

E

_

H

O

S

T

_

W

A

K

E

B

D19

B15

K

B

R

0

-7

K

B

C

0

-1

E3....

G3....

C13

MIDRATE1

P2

LCD RS

P1

LCD SDATA DATA(7)

M4

LCD CLK DATA(6)

N3

LCD CS

L3...

LCD DATA (0 - 5)

A14

DSL0

G11

DLL2

G10

DSL1

U11

HKSW

MUTE*

A13

HS INT

C14

S550

(Flip Open/ Close

Detect)

VPP_SIGNAL

D4

CS5

N13

(to Q1400)

(to J1300)

ADC DATA

D4

Q801

NEP IO REG

1

5

2

Light Sensor

4MB Ram

(from Neptune)

FLASH

Revision Overview

Rev. 1.0: Initial Block Diagram

Rev1.1: V400 product added,

updated RTC Batt. Connector to J1701,

added D700, removed Q1400 and R936

(not used anymore)

D700

VBUCK

D4

VBUCK

GSM SERVICE SUPPORT GROUP

2004.04.02

LEVEL 3 AL Block Diagram

Rev. 1.1

V30x, V400, V50x, V600

Michael Hansen, Alexander Buehler

Page 2of 2

(clock)

CLK 13 MHZ

E2

CLK 32KHZ

B6

TIMER

WDOG

T18

CNTL.

PRI SPI

LOGIC

Logic

A

A

1

1

,D

1

2

,

..

..

Y

1

8

S

w

it

ch

er

1

B

+

S

en

se

B

B

-S

P

I_

C

L

K

B

B

_

S

P

I_

M

O

S

I

B

B

_

S

P

I_

M

IS

O

P

C

A

P

C

S

CODEC

PHONE

R

1

1

V

1

0

W

1

0

W

1

1

E

3

H

7

J8

B

1

9

5

6

4

INTERF.

USB

D+

D-

USB PWR

Y900

B4

V16

RTC_BATT

B5

B+

to

V

ib

ra

2

13

14

RAW_OPT1

RAW_OPT2

HAND SPKR-

HAND SPKR+

HJACK_MIC

U1

R2

H2

J2

M3

N2

O

N

2

P

W

R

S

W

AUDIO_OUT

15

N1

ON2

Y

1

3

W

1

4

16

1

17-20

RAW_BATT_FDBK

RAW_EXT_+

3

SW B+

U901

B+

SW B+ EN

A9

C7

B7

7

U900

PCAP3

MEMORY

HOLD

BACKl.

CONTR.

ON

LOGIC

M1700

OWB

THERM

W6

THERM

2

3

RAW_EXT_B+

ISENSE

BATT+

AA20

Y19

V18

1

4

GND

BATT+

Q950

CHRGC

Y20

R

9

5

0

EXT_B+

S

G

D

CHARGE

CHARGER

BATT CONN.

AUDIO_IN

E1

CNTL.

LED

BATT FDBK

A

A

1

9

IO

R

E

G

Y

5

This resistor is IN the

Charger accessory and

is used for identification

Y12

V

IB

D

R

IV

E

BATTERY

B

B

S

A

P

F

S

B

B

S

A

P

C

L

K

B

B

S

A

P

T

X

B

B

S

A

P

R

X

(tx) (rx)

C

R

9

0

0

Neptune PCap

CODEC

16 BIT

STEREO

(tx) (rx)

Communication

ALERT-

ALERT+

PCAP_MCU_RESET*

Y20

STANDBY

R14

(to Neptune and U301 BT)

P

C

A

P

I

N

T

V

1

4

RESETB

(from Neptune)

CNTL.

SEC SPI

LOGIC

Neptune PCap

Communication

EXT_OUT

USB PU

R904

B9

Y3

AA3

Y4

AA2

TOUCH

SCREEN

INTERF.

Q952

S

G

D

B+

U21

MAIN_FET

VOLT.

OVER

CNTL.

Battery to B+

Switch

Q954

S

G

D

(Overvoltage Protection)

OV GATE

RAW EXT B+ to EXT B+

RAW EXT B+

R

9

0

5

( from/ to PCap)

8

( toPCap + Q954)

LOGIC SENSE

AD8

V6

(

AUDIO_IN

Sense)

W18

IO

Y7

THERMBIAS

A

D

6

U

S

B

V

P

IN

U

S

B

X

R

X

D

R

T

S

U

S

B

V

P

O

U

T

T

X

D

U

S

B

V

M

IN

R

X

D

U

S

B

T

X

E

N

B

U

S

B

S

E

0

USB/RS232

(communication)

D

8

C

9

A

7

B

8

G

8

C

8

13 BIT

FAIL DET.

POWER

INT_MIC_OUT

INT MIC BIAS

G2

W1

HJACK_SPKK

J1240

4

2

3

HJACK_DET

1

Headset

D

E

T

.

S

T

E

R

E

O

B

u

ck

M

o

d

e

F

1

8

(

1

,8

7

5

V

)

V

B

U

C

K

S

w

it

ch

er

2

B

u

ck

M

o

d

e

G

2

1

S

w

it

ch

er

3

B

o

o

st

M

o

d

e

B

2

1

(

5

,6

V

)

V

B

O

O

S

T

H

2

0

(

2

,7

7

5

V

)

I

O

R

E

G

Y

1

(

2

,7

7

5

V

)

A

U

D

IO

R

E

G

K

1

9

(

1

,2

7

5

)

G

A

1

.2

V

L

2

1

K

2

0

N

1

9

K

1

8

(

2

,7

7

5

V

)

R

F

R

E

G

V1

V2

V3

V4

V5

V6

V7

Q960

NEP IO REG

( 2,775V )

P

O

W

E

R

C

U

T

S

V

C

C

J2

1

M

2

0

(

1

,5

7

5

V

)

R

E

F

R

E

G

N

2

0

(

5

,0

V

)

R

F

5

V

R

E

G

V8

V9

V10

E2

C

1

2

(

1

,8

/

3

V

)

V

S

IM

V

S

IM

V

S

IM

_

E

N

G

1

1

AUDIO

AMPL.

EXT B+

BATT_FDBK

13

12

D+

D-

24

22

1

3

J1701

GND

CONTR.

BATT DETB

Y6

NC

NC

D4

B3

(to

SIM PD

)

BATT.

AD

EXT B+

U20

R

9

0

6

IO

R

E

G

(B

ia

s)

(One Wire Bus

to Neptune)

VR951

L950

PA B+

NC

NC

NC

NC

S

4

G

D

3

2

MIDRATE 1

Q953

Q951

EXT B+ to B+

Switch

SWITCH

(from Neptune)

(Key Source

for PCap IC)

(to EAGLE IC)

(from Acesory Connector)

(to PCap AD Converter

(to PCap AD Converter)

and internal Charger)

Main Charge Path

B+ support without Ext Charger

B+ support with Ext Charger

Color definition only for this section !

VR950

N

C

BB SAP TX

BB SAP RX

BB SAP FS

BB SAP CLK

(framesync)

N

C

N

C

Bluetooth

U301

32

30

28

27

BLUE_WAKEB

11

BLUE_HOST_WAKEB

9

BLUE_TX

5

BLUE_CTS

BLUE_RTS

31

BLUE_RX

33

29

BLUE_RESETB (RESETB)

22

(from Neptune/ PCap)

(from/ to Neptune

Serial Audio for Ringtone

and Voice Audio)

NEP_IO_REG

10

BTRF_REG

21

ANTENNA

25

Strip Line

Antenna

(on PCB)

R

9

0

6

Y300

15

16

BLUE_CLK_ENB

13

(

1

,8

V

)

B

T

R

F

_

R

E

G

N

C

Q924

S

G

D

N

C

(VCC)

(Enable)

2

3

V

V

IB

(

to

V

ib

ra

to

r

in

F

li

p

)

(from Neptune)

(

1

,8

V

)

Neptune PCap

N

C

N

C

N

C

N

C

N

C

N

C

N

C

N

C

Neptune PCap

USB/ RS232

Communication

23

C3

B2

BL FB

BL SINK

R1459

1

2

AD TRIG

W19

(from

EXC EN

- (trigger))

(Over Volt. Sense)

(Battery Sense)

(External B+ Sense)

W21

MIDRATE2

(from Neptune)

K2

MIC BIAS 2

IO

H

J

A

C

K

_

D

E

T

K

7

CONV.

D/A

CLK 32KHZ

(from PCap)

(to Neptune)

(to PCap)

(to PCap IO)

J1200

A, B

Jack

J1400

CE

Conn.

J1260

1

2

OPT1

OPT2

5

6

20

19

10

11

RAW_DSEL2

RAW_DSEL1

DSEL2

DSEL1

9

8

16

17

12

RAW_DSEL0

DSEL0

7

18

( to Neptune)

RAW_HKSW

RAW_MUTE*

14

15

HKSW

MUTE*

11

10

J1300

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

HAND SPKR+

HAND SPKR-

GND

LCD DATA(0)

RESET OUT B

GA INT

LCD RS

CLK 32KHZ B

GND

GND

GND

GA SPI CLK

GND

GA SPI MISO

GA SPI CS

GA SPI MOSI

GND

LCD DATA(1)

LCD DATA(2)

LCD DATA(3)

LCD DATA(4)

LCD DATA(5)

LCD CLK DATA(6)

LCD SDATA DATA(7)

LCD CS

ATI 1.8V( VBUCK)

PA B+

GND

GA 1.2V

GND

FUN SPI CS

IO REG

GND

VVIB

KEYPAD

MATRIX

R

1

9

(from PCap)

(from PCap 1,3V from Vibrator Regulator)

(

1

,3

V

)

VBOOST

R1450- R1457

D1450- D1457

BL SINK

KBC0 -1

KBR1 -7

PWR SW

POWER/END

S513

0-9,*,#,

Up, Down

Left-Right,

Center,

Soft L+R,

Menu, Send,

Volume U-D

Smart, VA

GND

(from/ to U301 BT,

Neptune - BT - Neptune

Communication and Wakeup)

FLIP

CONNECTOR

BACKLIGHT

LED´s

FL1400

ESD Protection

Internal

MIC

Alert

Speaker

Only V50x and V600

(RXD2)

(TXD2)

(RTS2)

(CTS2)

Revision Overview

Rev. 1.0: Initial Block Diagram

Rev1.1: V400 product added,

updated RTC Batt. Connector to J1701,

added D700, removed Q1400 and R936

V30x, V400, V50x, V600

Wyszukiwarka

Podobne podstrony:

BD C150 L3 C A3 V1[1] 2

BD TripletsR L3 C A3 V1[1] 1

BD Z3 L3 C A3 V1 1

BD V3 L3 C A3 V1[1] 2

BD C200 L3 C A3 v1[1] 0

BD U9 L3 C A3 V1 0

BD F3 L3 C A3 v1

BD K1 L3 C A3 V1 3

BD BlDi V235 L3 C A3 V1[1] 1

Block Diagram W510 L3 C A3 V1 0 Block Diagrams

Block Diagram V3 06 L3 C A3 v1 0

BD W206 W213 A3 C L3 V1

C380 PCB P4c L3 A3 BW V1 0

BL C380 P4c L3 A3 BW V1[1] 0

BL C650 P03 L3 A3 BW V1(1)

BD BlDi E365 A3 C L3 1[1] 2 030611100711

SCH C650 P03 L3 A2 C V1[1] 1

więcej podobnych podstron