K1

3

3

2

2

1

1

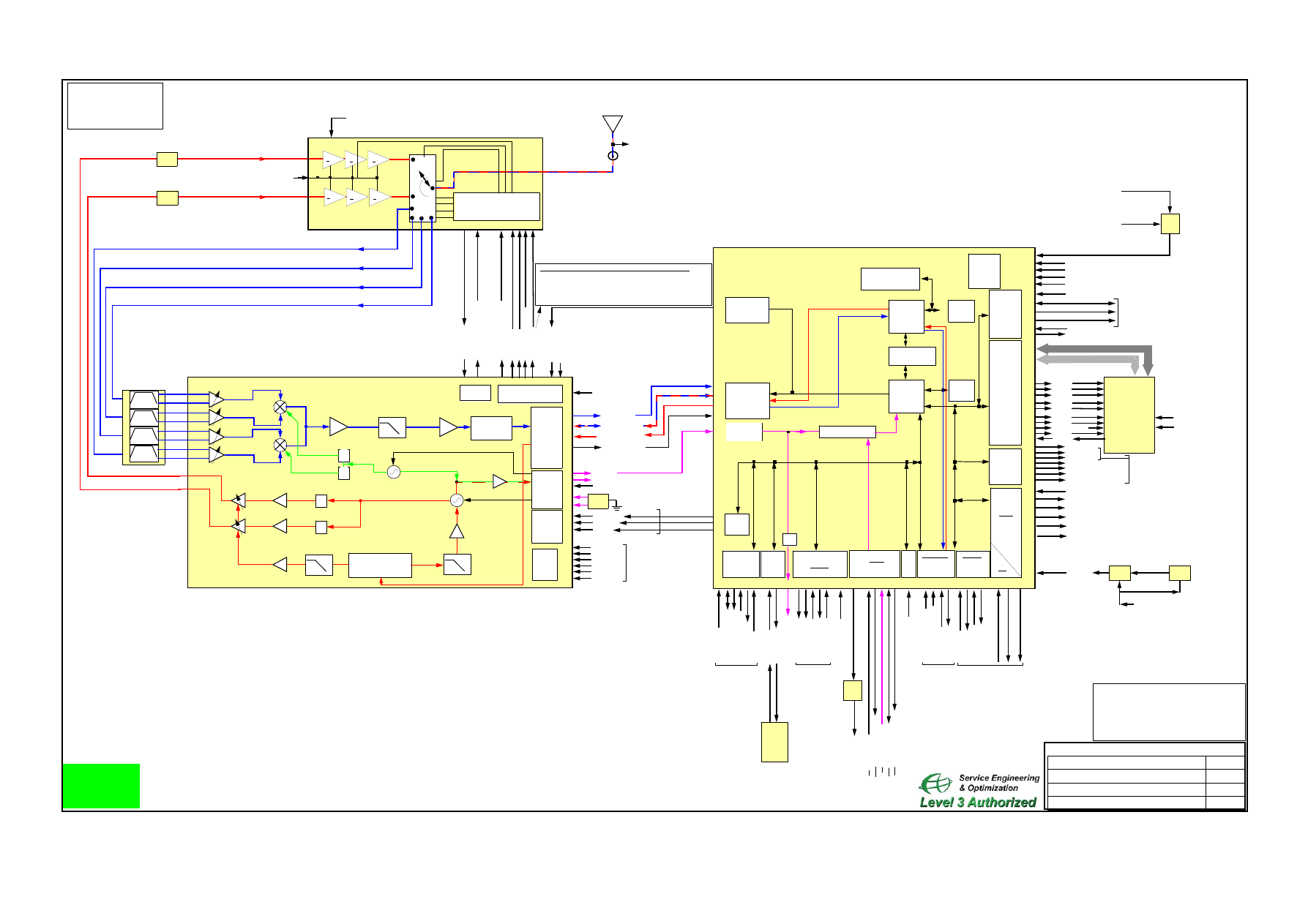

LNA

LNA

LNA

TX_HB

DCS/PCS OUT

GSM850/

BP

15

11,14....

26

25

GSM900 OUT

Se

ria

l

Inte

rface

D1

E3

G3

1

U50

PA + Antenna Switch

6

13 8

E1

D2

F1

MISOB

MS

MDI

DRI

VRA

M

P

Y201

26MHz

2

1

1800 MHz

1900 MHZ

850 MHz

900 MHz

(P

A Po

we

r Contr

o

l)

J7506 Mechanical

Antenna Switch

Internal

Antenna

M1

RES

E

T

B

US_

E

U

R

O

TX_

A

N

T

_S

W_

EN

TX_

S

T

A

R

T

F3

(T

ra

ns

m

itt E

n

able)

RF_CLK

RF_DATA

RF_CS

B3

PA Control

B9

C2 A2

E2

GPIO

(U250 Control Bus)

ADC

Voltage

Reg.

VM_REG

VBUCK

RF_REG

J5, J8

H2

B4

(VCC’s from Atlas)

A4

1Mbit RAM

DSP

DSP

UltraLite

104 MHz

DSP Peripherals

accelerator, encryption

Timer, Interupts

Shared Memory

MCU

52 MHz

ARM7

MCU

26 MHz

Oscillator

Memory

Memory

SIM

Interface

External

Interface

Memory

N10

Clock Generator

SPI

Power

NEPTUNE LTE2

U800

W10

U9

T8

GPIO

L1 Timer

U6

U8

V7

W9

UART / USB

Interface

Keypad

Interface

On

Off

SIM DIO

SIM RST

SIM CLK

SIM_PD

VSIM_EN

VBUCK

(VCC + 1,875V)

(from Atlas )

VSIM

(to Atlas)

IO_REG

J4

L1

K3

R1

M1

K2

(from Atlas )

PERIPH_IO_REG

EGSM: CH 37 -- 942,4Mhz

DCS: CH 700 -- 1842,8MHz

PCS: CH 661 -- 1960MHz

RX MID CHANNELS

GSM: CH 62 -- 947,4 MHz

850: CH190 -- 881,6

MQSPI

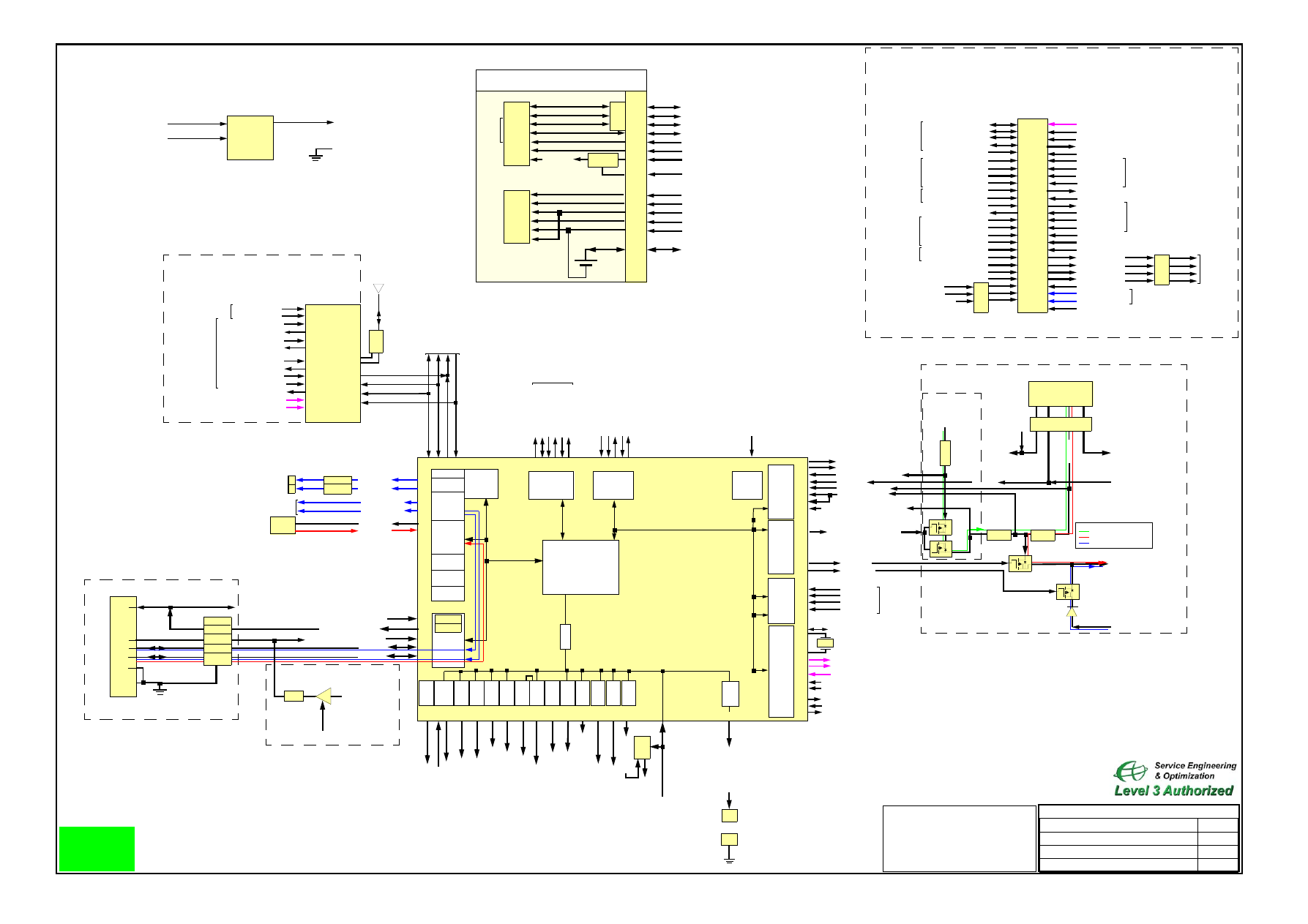

Display

U700

EB1B

EB0B

OEB

R_WB

CS1B

ADDRESS BUS

DATA BUS

K16

J19

G17

T16

BURSTCLK

LBAB

CS0B

ECBB

V17

T19

L16

N18

A0-23

D0-15

64 MB Flash

RESET OUT

F3

C2

G8

E5

F5,D5

J2,H1,H8

G7

C6

K1

F4

D6

HS INT

C14

TF_ENABLE

16 MB SRam

(from Neptune)

FLASH

U13

BB

_SA

P

_T

X

B

B

_

S

AP

_R

X

BB

_SA

P

_

F

S

BB

_S

A

P

_

C

LK

B13

B12

A12

D13

(fram

es

y

n

c)

(cl

o

ck)

CLK

13 MH

z

W13

C15

C16

D15

A16

BB

_

S

P

I_C

LK

BB

_S

PI_M

O

S

I

B

B

_S

PI_

M

IS

O

AU

L_

CS

Neptune Atlas

Communication

T11

V12

V11

W12

ST

AN

DB

Y_1

_5V

G8

ST

A

N

DB

Y

CL

K 32

KH

Z

E3

B14

AU

L_

INT

RE

SET

B

V13

(13 M

H

z)

(W

a

tchdog)

WD

OG

OW

B

W11

On

e W

ire dat

a from

B

at

te

ry

US

B_V

P

IN

U

S

B

_

XR

XD

_

R

T

S

US

B_V

P

O

U

T

_

TX

D

US

B_V

M

IN_R

XD

U

S

B

_

TX

EN

B

US

B_S

E

0

B16

A17

Neptune Atlas

USB/ RS232

Communication

(t

o At

las

)

RE

SET

O

U

T

W5

(t

o U700)

(from/ to Neptune

Serial Audio for Ringtone

and Voice Audio)

BL

UE

_R

X

B

L

U

E

_T

X

B

L

U

E

_R

TS

B

B

L

U

E

_C

TS

B

N17

N13

V16

D16

(from/ to U301 BT, J1300

Neptune - BT - Neptune

Communication and Wakeup)

BLU

E_

W

A

KE

B

B

L

UE

_H

OS

T_W

A

K

E

B

D19

B15

KB

R0

-7

KB

C

0

-2

F3....

F2....

Timer

GPIO

Interface

BaseBand

Port Interface

Serial Audio

(tx)

(rx)

MQSPI

One

Bus

Wire

UART2

Universal

Asynchron.

Rx /Tx

BT

CS2B

W18

W8

T10

G

RAP

H_

INT

9

LB_

HB

C3

TX

_E

N

2

3

4

Power and

Antenna

Control

16

A1

3

K4

K5

LNA

TX_LB

L8

L10

2

4

(fro

m A

tl

as

)

VBUCK

E4...

(from

Atlas

)

U801

Level

(t

o Atlas

)

P2

LCD_RS

P1

LCD_SDATA_DATA7

M4

LCD_CLK_DATA6

N3

LCD_CS

L3...

LCD DATA (0 - 5)

(LCD Control to J2 )

U1401

4

5

Hall Effect

Inverter

Shift

(VCC + 1,575V)

REF_REG

E2

A

TI_

RES

E

T

B

_2

_7V

U11

(t

o

J

2

)

(VCC + 2.775V)

A11, U16, .....

(VCC + 2.775V)

H1

V5, R16, ....

TOUT12

U10

(Bias output for THERM signal)

(Clock )

(Reset )

(Data In /OUT)

(T

rans

mit

t E

n

abl

e

)

(Clock )

(Chip select)

(Data In /OUT)

10

(fro

m A

tl

as

)

T18

(Trans Flash Enable to J27 )

ANT_DET_B

(indicates mechanical Antenna connection to U800)

ANT_DET_B

U12

(indicates mechanical Antenna connection to U800)

EL_EN

N9

(EL Backlight Enable to U1501)

17

IPC

_

BC

M

B2

VCO_REG

18,31

FL82

FL54

2

2

4

4

FL100

Quard Saw Filter

4

3

Low Band

850MHz

Low Band

900MHz

High Band

1800MHz

High Band

1900MHz

6

1

and Matching

14

15

12

13

8

9

10

11

K12

L12

G12

H12

A12

B12

D12

E12

DC

Correct

LPF

÷

4

90°

÷

2

90°

÷

2

÷

2

LPF

LPF

Transmit

Modulator

TX CP

RX CP

Phase Modulation

Amplitude Modulation

TX VCO

RX VCO

VCO_REG

C10

IO_REG

C1

Digital Radio

Receiver

Synt

hesize

r

RX /

TX

Cl

ock

RX /

TX

In

/ O

u

t -

P

u

t c

o

n

tr

o

le

r

MCLK

G2

(Data TX)

(TX/RX Enable)

(Data RX)

(readback)

J1

BT_CLK

J3

BT_CLK_EN

G1

STANDBYB

VD

ET

EC

T

A4

REF_1p2

C5

D18

LCD_WEB

B

T

_

R

ES

ET

_B

T7

(from / to J24_DB)

TX_EN_SW

V8

(to Atlas U900)

EMU_HDST_DET

A12

(to Atlas U950 )

5,6

3

U807

2

IO_REG

BP

REG_BYP_CORE

Switch

M18

(Flip Open/ Close

Detect)

1

6

PERIPH_IO_REG

U1600

2

Servive, Engineering & Optimization

2006.12.1

LEVEL 3 AL Block Diagram

Rev. 1.3

K1

Page 1of 2

Key-Matrix

0-9,*,#

Navigation,

Smart,

Volume

(from

J

500

0 v

ia J

2

)

D14

LCD_OE

Synthesizer

U250

Revision Overview

Rev. 1.0: Initial Block Diagram

Rev. 1.1: updated U700 Memory size

Rev. 1.2 updated MISOB information,updated information at

U950 Headset detect circuit, updated information at U50 /

IPC_BCM

Rev. 1.3: RX signal name#s change + Pins on U50

(only used in Engineering debug mode

1. IPC: Input Power Control mode - for EDGE mode

2.BCM: Bias Control mode - for GMSK mode

(PA gain is fixed and PA input power varies)

(PA gain varies according to power step and fixed input PA power)

PA Power Control selection via VRAMP, TX_HB and TX_LB

- not for Service)

Revision Overview

Rev. 1.0: Initial Block Diagram

Rev. 1.1: updated U700 Memory size

Rev. 1.2 updated MISOB information,updated information at

U950 Headset detect circuit, updated information at U50 /

IPC_BCM

Rev. 1.2: RX signal name#s change + Pins on U50

Servive, Engineering & Optimization

2006.12.1

LEVEL 3 AL Block Diagram

Rev. 1.3

K1

Page 2of 2

K1

40

38

36

34

32

30

28

26

24

22

20

18

16

14

12

10

8

39

37

35

33

31

29

27

25

23

21

19

17

15

13

11

9

7

LCD_DATA7

LCD_DATA4

LCD_DATA1

GRAFX_REG_FL

CAM_AVDD_FL

LCD_DATA2

LCD_WEB

CAM_DIG_REG_FL

IO_REG

ATI_RESETB_2_7V

LCD_DATA3

LCD_DATA0

LCD_DATA5

LCD_DATA6

HAND_SPKRM

HAND_SPKRP

BB_SAP_RX

BB_SAP_TX

BB_SAP_CLK

BB_SAP_FS

PERIPH_IO_REG

GND

GND

BLED_SINK4

BLED_SINK3

BLED_SINK1

6

4

2

LEDB1

VBUS

CHRGLED

g1- g4

GND

5

3

1

GND

(to Atlas)

(from Atlas)

(from Neptune)

J2

FLIP CONNECTOR

Flip Connector

GND

GRAPH_INT

LCD_OEB

LCD_CS

LCD_RS

VBUCK_FL

VBOOST

(clock)

CLK 13 MHZ

V12

CLK_32KHZ_2_7V

P16

TIMER

WDOG

K10

CNTL.

PRI SPI

LOGIC

Logic

F3

,E

1

3

....

...

.

S

w

it

cher

BB

-SP

I_C

LK

BB

_SP

I_M

OS

I

BB

_SP

I_M

IS

O

AUL

CS

U1

8

U1

6

T1

8

T1

7

R5

Interface

USB

Y900

V17

D12

RTC_BATT

V16

BP

HAND_SPKRM

HAND_SPKRP

T6

R7

T9

P9

V10

U8

PW

R_S

W

F14

B4

E3

F3

U900

ATLAS UL

ON

LOGIC

OWB

THERM

P13

THERM

BATTP

D14

GND

CHRGCTRL

B16

VBUS

S

G

D

CHARGE

Charger

BATT CONN.

CNTL.

LED

E12

B

B

_S

AP

_FS

BB

_S

A

P

_

C

LK

BB

_S

AP_

T

X

BB

_SA

P

_

R

X

CODEC

16 BIT

STEREO

(tx) (rx)

ALERTM

ALERTP

STANDBY

F12

(to Neptune and U301 BT)

A

U

L_

INT

N1

4

RESETB

(from U800)

Neptune Atlas

Communication

USB_ID

H8

Q904 (M3)

G

S

BP

B12

BATTFET

Battery to BPLUS

US

B_V

P

IN

U

S

B

_

XR

XD

_

R

T

S

US

B_V

P

O

U

T

_

TX

D

US

B_V

M

IN

_R

XD

U

S

B

_

TX

EN

B

US

B_S

E

0

USB/RS232

(communication)

B2

C4

F4

B1

B3

E4

MICINM

MICBIAS1

Det.

Stereo

B

oos

t 300mA

G1

6

S

w

it

cher

B

u

ck 350

mA

F1

6

( 1,

87

5V

)

VBU

C

K

H2

( 2

,77

5V

)

P

E

R

IPH

_IO

_

RE

G

U6

( 2,

7

75V

)

AU

D_ R

E

G

M1

8

( 1,

27

5 )

G

R

AF

X_

R

E

G

K1

7

H4

H3

( 2,

77

5V )

RF

_

R

E

G

L1

6

( 1,

57

5V

)

RE

F_

REG

N5

( 1,

8

/ 3V

)

VS

IM

VS

IM_

E

N

K1

1

VBUS

CONTR.

AD

C15

PE

RIP

H

RE

G

(B

ia

s)

(One Wire Bus

to Neptune)

BPFET_PM

VBUS to BP

Switch

(Main Source

for Atlas)

(from Mini USB Connector)

Main Charge Path

B+ support without Ext Charger

B+ support with Ext Charger

Color definition only for this section !

D903

BB_SAP_TX

BB_SAP_RX

BB_SAP_FS

BB_SAP_CLK

(framesync)

Bluetooth

U301

C7

BLUE_WAKEB

C8

BLUE_HOST_WAKEB

C6

BLUE_RX

E5

BLUE_CTSB

BLUE_RTSB

E7

BLUE_TX

E4

E8

BT_RESET_B

E3

(from/ to Neptune

Serial Audio for Ringtone

and Voice Audio)

PERIPH_IO_REG

B3......

BP

H6

BT_

AN

T

25

Strip Line

Antenna

(on PCB)

F6

VV

IB

(from Neptune)

NeptuneAtlas

Neptune Atlas

USB/ RS232

Communication

(Battery Sense)

(VBUS Sense)

CONV.

D/A

CLK_32KHZ

(from Atlas)

3

(from Atlas)

( 1,3

V

)

(from/ to U301 BT,

Neptune - BT - Neptune

Communication and Wakeup)

Internal MIC

PCB

Pads

TX_EN_SW

U15

(from Neptune, Tx Mode indication for Atlas)

( 2,

77

5 )

IO

_R

E

G

( 2,

7

75 )

C

A

M

_

A

VDD

( 5,

5V

)

VB

O

O

S

T

2

3

VBUS

1

4

5

(to Charging Circuit)

G1-G4

(Shield)

CLK_32KHZ

R16

DM_TXD

DP_RXD

VBUS 5V

Pass FET

VBOOST

VBUS

D2

(PPD device support)

(from J1300)

(to J1300)

to V

ibr

ator

VIB REG

P2

Mo

to

r

REF REG

RF

R

E

G

PE

RI

PH

IO R

E

G

AU

D

IO

REG

IO REG

GR

A

P

H

REG

CAM

E

RA

REG

P18

DIG

REG

4

Microphone

R3

P4

R4

(tx

)

(rx

)

13 Bit

Handset

Amplifier

(to J2)

Q91

0

VC

O

REG

VC

O_D

R

V

(M

ain Sour

ce-

f

rom Q

904)

( 2

,775

V

)

V

C

O

_RE

G

V2

SIM_PD

T14

CHRGRAW

S

G

D

Q903 (M4)

Q905 (M1)

G

S

R910

R911

D

Switch

B14

CHRGISNSP_PM

E15

(Current Control)

Q906 (M2)

(only

us

ed i

n

Atlas

)

C6

BLED_SINK1

(t

o Ne

p

tune)

(t

o J

2,

J1000, Q2020)

(t

o Neptun

e

am

d J

2

7)

(t

o U250)

(t

o J

2, J

1

000, J

2000)

(t

o AL

+

R

F

))

(t

o U50,U25

0)

Bluetooth

Mini USB

Charger and Power-

source Control

(to Neptune, U250)

(toNeptune)

(from Atlas)

(from Neptune)

TOUT12

(Bias Voltage from

Neptune)

(Accessory Detection signal)

(from Acesory Connector)

(EXT Power)

(EXT Power)

Det.

Headset

(from FL3001)

R9

05

3

4

1

ESD

VR1212

VR960

VR1203

VR1212

SAP

Supply

Amplifier

Alert

Amplifier

Headset

Amplifier

EMU

J1

NC

NC

ALERT

NC

ESD

FL1400

SDC0DQ0

SDC0DQ2

46

44

42

SDC0DQ3

SDC0DQ1

GND

50

48

49

47

45

43

41

CLK_32KHZ_2_7V

GND

GND

SDC0CLK

BLED_SINK3

(from Atlas)

1

2

BA

T

T

P

J3

2

3

1

4

VR1201

B

+

Sens

e

(t

o J

2

)

(t

o J

2, J

1000, D1

000

ISNS

F13

(Batt Current)

(Charger Current + )

( 1,

8V

)

CA

M_

DIG

_

R

E

G

M1401

1

2

U14

CHRGLED

L10

(toFL3002)

STANDBYB

P14

(to U250)

B6

BLED_SINK2

D6

BLED_SINK3

F8

BLED_SINK4

H3

(2,

7

75V

)

VM

_R

EG

(t

o U250)

VS

IM

RF

R

E

G

(f

ro

m

U800)

(t

o AL

+

R

F

))

(to

A

L

+

R

F

))

J3500, U1

501)

JVIB

R17

REF REG

( 1,

2

V

)

RE

F_1

P

2

(t

o U250)

U950

R950

PERIPH_IO_ REG

EMU_HDST_DET

(Headset detect Enable from Neptune)

(Bias from Atlas)

(100K Headset

(LCD Data from Neptune)

from/ to Neptune)

FL3001

(from Atlas)

(Control Bus for ATI

GND

SDC0CMD

(SD Card Command from U5000)

(SD Card Clock from U5000)

GND

FL30

02

(from Atlas)

(from J1)

(from Atlas)

(fitered VCC from Atlas)

(from Atlas)

(LCD Control

from Neptune)

(fitered VCC from Atlas)

(interupt from U5000

to Neptune)

(LCD Data from Neptune)

(SD Card Data

from/ to Daughter

STANDBY

C4

BT_CLK_EN

D7

(to U250)

A7

B6

C7

FL

301

H1

H2

Board Conn. J27)

J27

SDC0DQ2

SDC0DQ3

SDC0CMD

SDC0CLK

1

3

5

9

11

13

SDC0DQ0

SDC0DQ1

Daug

h

ter Boar

d

Connect

or

FL120

0

PERIPH_IO_REG

7

J6

T

ransflash

7

8

1

2

3

5

4

TF_VDD

TF_ENABLE

12

Q2000

G1-G3

GND

J4

SIM

1

2

3

4

5

6

SIM_DIO

SIM_CLK

VSIM

SIM_RST

GND

8

2

6

4

14..

10

+

RTC_BATT

RTC

BATT

Daughter Board

EL_EN

EL_LAMP_VP

EL_LAMP_VM

VBOOST

8

3

10

U1501

EL Driver

E2

BT_CLK

(from U250)

detect Resistor)

Headset detect circuit

Wyszukiwarka

Podobne podstrony:

BD V600 L3 C A3 V1[1] 1

BD C150 L3 C A3 V1[1] 2

BD TripletsR L3 C A3 V1[1] 1

BD Z3 L3 C A3 V1 1

BD V3 L3 C A3 V1[1] 2

BD C200 L3 C A3 v1[1] 0

BD U9 L3 C A3 V1 0

BD F3 L3 C A3 v1

BD BlDi V235 L3 C A3 V1[1] 1

Block Diagram W510 L3 C A3 V1 0 Block Diagrams

Block Diagram V3 06 L3 C A3 v1 0

BD W206 W213 A3 C L3 V1

C380 PCB P4c L3 A3 BW V1 0

BL C380 P4c L3 A3 BW V1[1] 0

BL C650 P03 L3 A3 BW V1(1)

BD BlDi E365 A3 C L3 1[1] 2 030611100711

SCH C650 P03 L3 A2 C V1[1] 1

więcej podobnych podstron