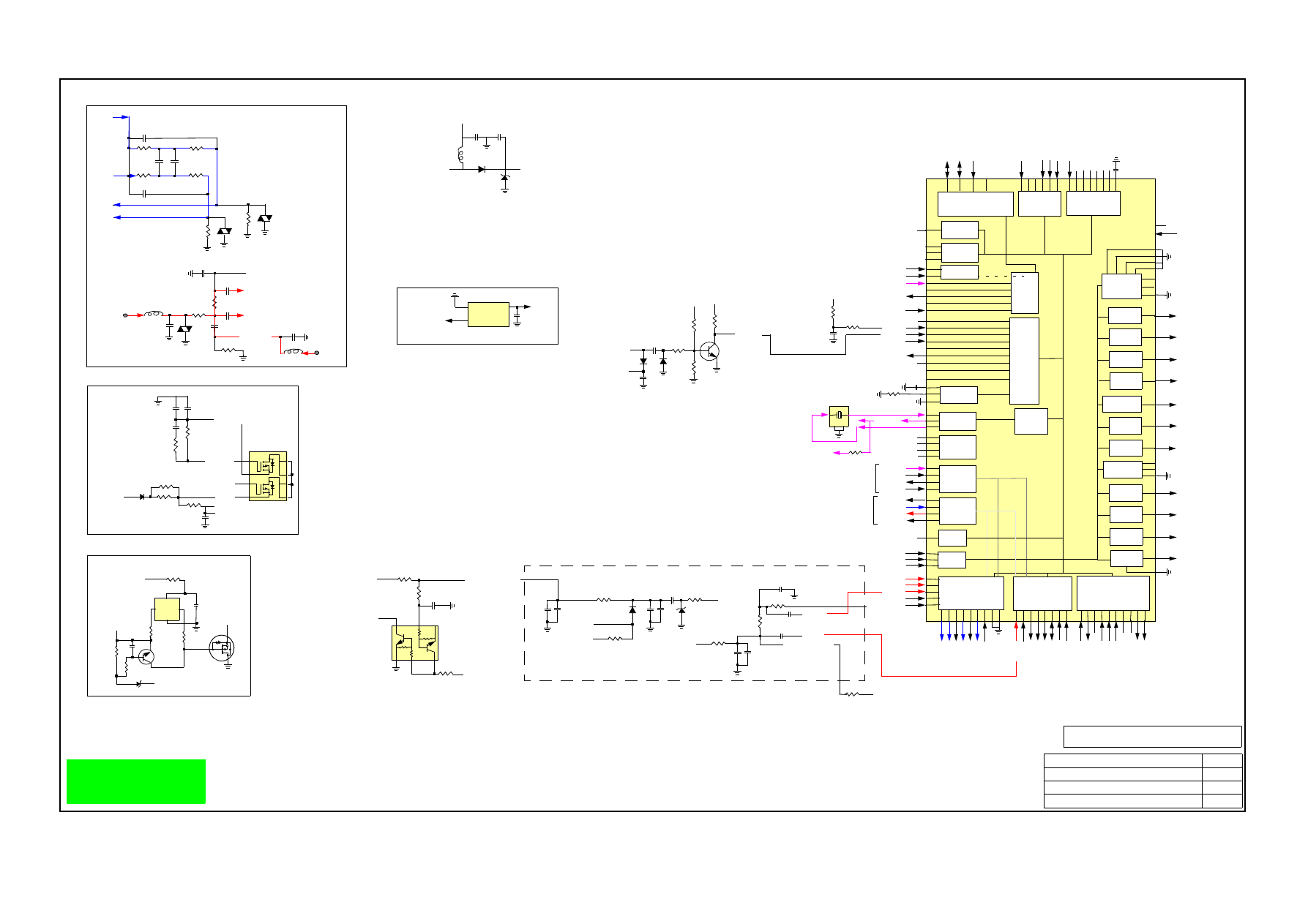

F3

GSM SERVICE SUPPORT GROUP

2006.09.29

LEVEL 3 Block Diagram

Rev. 1.0

F3

Page1of 3

Revision Overview

Rev. 1.0: Initial Block Diagram

1

4

2 3

Y2

(32.768KHz)

OSC32KOUT

SIM Card

Interface

Ext Port

I2C

External LDOs Control

Headset Detection

Precharge Boot Mode

M-ADC

USB OTG

Transceiver

VRDBB

(Stepdown

DCDC)

BUS

Control

Power

Control

State

Machine

Vref

Iref

OSC

32-KHz

Real Time

Clock

Test IF

I2S

VSP

Voice Codec

Stereo Codec

LED

Driver

Vib

Driver

Battery

Charger

Interface

VRPLL

(LDO)

VRMEM

(LDO)

VRABB

(LDO)

VRIO

(LDO)

VRWLED

(Stepup DCDC)

VRRTC

(LDO)

VRUSB

(LDO)

VRVBUS

(Stepup DCDC)

VRSIM

(LDO)

VRMMC

(LDO)

VREXTH

(LDO)

VREXTL

(LDO)

U601

M11

CKOUT_13MHZ

M10

NC

M8

VRTC

K12

NC

T14

PWON

U13

RPWON

M12

WAKEUP

U15

ONnOFF

T15

NC

M16

C604

L12

R601

M17

R16

P16

CLK32K

T16

U1

NC

U2

T1

R1

NC

NC

NC

(TDI)

(TDO)

(TCK)

(TMS)

(PCLKREQ)

(SIMDTC)

(TESTRESET)

T7

I

2

S_SCK

T6

I

2

S_SDR

I

2

S_SDX

I

2

S_WS

U5

U6

T3

VSP_VCK

T4

VSP_VDR

VSP_VDX

VSP_VFS

T2

U3

U12

NC

(VIBDR)

C16

E17

F17

LED_A

LED_B

LED_C

MICIN

MICIP

F2

G2

HSMIC

D2

G6

H6

MICBIAS

HSMICBIAS

H2

J2

EA

R

N

EA

R

P

M1

..

SP

K

N

D

SP

KN

A

SP

K

P

D

SP

KP

A

M6

..

K1

..

K6

..

H1

N1

L1.

.

VB

C1

AUX

I

C2

FM

L

G1

F1

HSO

L

HSO

R

J6

HSO

V

M

ID

E1

AU

D

V

M

ID

P2

FIL

T

ER

APL

L

B1

1

HS_

S

P

K

_C

HA

RG

E

A12

A1

1

PC

HG

A

C

NC

(P

CHGUSB)

A10

VCC

S

B1

2

VBA

T

B1

0

VB

A

T

S

A13

B1

5

NC

(I

CT

LU

S

B

1

)

(I

C

TLU

S

B

2

)

NC

F1

1

F1

2

ICT

L

A

C

1

ICT

L

A

C

2

G16

VEXTL

G17

L17

VEXTH

T10

VMMC

VSIM

A3

F9

B8

VUSB

N17

VRTC

B14.

B15

VWLED

J16

B2

U11

T12

VIO

VABB

(NC)

VMEM

VPLL

J12

T9

U8

A6

D16, C17

A5

C

410

A7

A8

NC (

D

M

_

T

XD_S

P

KR_L

)

NC (

D

M

_

T

XD_M

IC_R)

F6

NC

(

R

C

V

_T

E

S

T

4

)

B6

B4

B3

B9

VB

US

NC (

S

E

O

_VM

_

T

XD_T

E

S

T

3)

NC (

D

A

T

_VP_RXD_T

E

S

T

2

)

N

C

(O

E

_

IN

T

N

_

T

ES

T1

)

F8

F7

B7

VD

CI

N

5

V

DCI

N4

V

DCI

N3

M9

ST

AR

T

A

DC

R17

VBACKUP

F1

6

HS

DE

T

U7

I

2

C_SDA

G1

2

H1

2

CK

E

N

RE

GE

N

B17

NC

(TESTV)

T8

I

2

C_SCL

TRITON

C534

R519

C323

C536

HSMIC

AUXI

ACCESSORY_ID

C321

C

322

R334

HSMIC_OUT

R331

HSOL

VS301

C535

C31

7

C

318

HSDET

VBAT

R351

D404

R521

C35

7

C3

56

HEADSET

C313

R329

C32

0

C3

19

R332

C316

R330

R333

EARP

EARN

SPKPA

SPKNA

R324

R

V

304

R323

R64

1

C526

C527

R620

C627

MICBIAS

MICIP

MICIN

R509

MIC_GND

R350

R

V

30

3

C309

L302

TP647

C325

TP301

(Mic Pad)

(Mic Pad)

HANDSET

R414

VBAT

R401

C635

VBAT

VWLED

VLED

VR403

C402

C401

L401

VR401

ADCIN4

(to U601, ADCIN5)

(from U200)

(to U200)

(t

o U20

0

)

(from U200)

(f

rom U20

0

)

R2

P1_INT2

(to U200)

(t

o/f

rom U200)

HS_SPK_CHARGE

VBAT

R423

R421

C451

Q406

VBAT

R416

BATID

VBAT

1

2

3

M401

VBAT

RPWON

R413

Q403

VIO

R403

R418

D403

R419

D401

C405

VBACKUP

VBAT

R404

(to U601)

(from U601)

(t

o Headset)

(fr

om H

eads

et)

(f

ro

m M

401,

(T

emp

S

ens

or)

HSDET

(to U601)

(to U601)

(to U601)

(to U601)

(to U601)

Battery Jack

(from U601)

(To J1)

C619

C618

C620

R603

ICTLAC1

HS_SPK_CHARGE

G1

S1

D1A

D1B

D2A

D2B

G2

S2

U645

ICTLAC2

VCCS

R341

R605

R606

U641

PCHGAC

VBATS

VBAT

CHARGE

2

5

1

3

U640

Q404

R647

R405

R646

C647

C342

R406

VBAT

HSSPK_CHG_N

R407

HS_SPK_CHARGE

HSSPK_CHG_N

U644

VR402

PROTECTION CHARGE

(to U601)

(detection of accessory insertion)

(t

o/

fr

o

m U200)

B

att

e

ry I

D

)

(from U601)

(from U601)

(t

o

U645)

(to M401, to charge up Battery)

(feedback Voltage)

(from U601)

(B

att

C

h

ar

ger

I

/P

)

(P

re

-c

h

arg

e O

/P c

u

rr

en

t)

(c

h

ar

g

e C

u

rr

e

n

t Se

n

se

)

(c

h

arg

e

C

u

rr

en

t

Se

n

se

)

(m

a

in B

at

t voltage s

ens

e)

(t

ra

n

sis

to

r c

o

n

tro

l)

(t

ra

n

sis

to

r c

o

n

tro

l)

(driver O/P for Screen)

(driver O/P for Keypad)

(driver O/P for Aux Screen)

(Boot mode select, ‘1’ for Locosto)

(detection of power-on button depressed)

OSC32KIN

(to U200)

DISPLAY_32K

(to J1)

L301

(from U601)

(from U601)

(to J1)

(to J1)

(from J1)

(A

udio Fi

lter

Gnd

)

(c

lock r

esour

ce enable)

(N

C

)

(A

nalog)

(A

nalog)

(D

igit

a

l)

(D

igit

a

l)

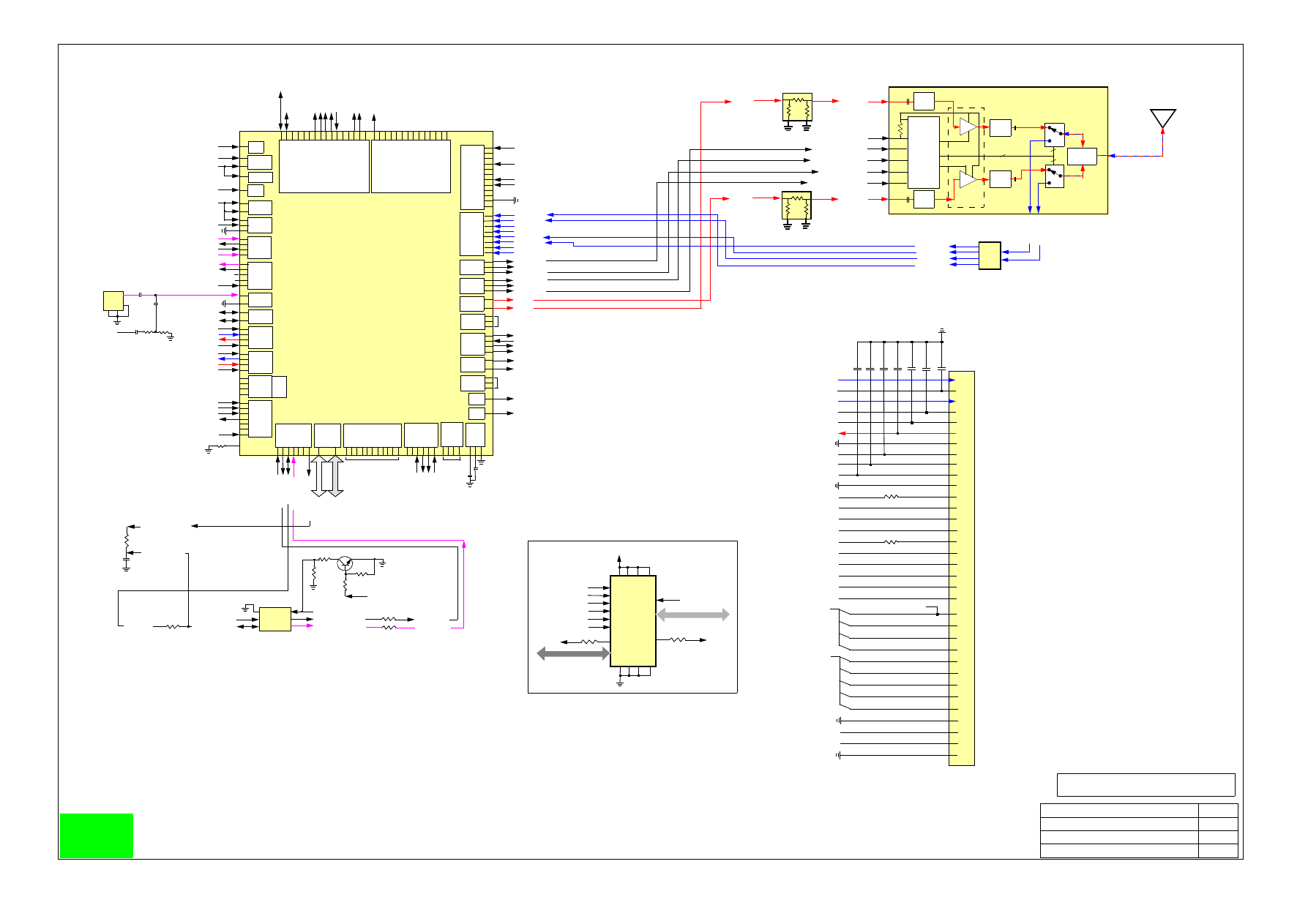

F3

GSM SERVICE SUPPORT GROUP

2006.10.05

LEVEL 3 Block Diagram

Rev. 1.0

F3

Page 3of 3

Revision Overview

Rev. 1.0: Initial Block Diagram

C3

30

C33

2

C33

3

C33

4

C

335

C3

36

C33

7

SPKPA

TEMP_SENSOR

SPKNA

DISPLAY_BUSY1

HS_SPK_CHARGE

HSMIC_OUT

VLED

HSSPK_CHG_N

LED_C

DISPLAY_32K

R346

DISPLAY_BUSY0

SYS_nCS0

SPI_CLK

SPI_MOSI

R347

SPI_MISO

SPI_MOSI

VIO

VBAT

PWON

KBR(0)

KBR(0:3)

KBR(1)

KBR(2)

KBR(3)

KBC(0)

KBC(0:4)

KBC(1)

KBC(2)

KBC(3)

KBC(4)

PCHGAC

RF_ANT

J1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

A-KEYPAD

VPLL

DRR_VR2

DRR_VR1

VRIO

Nand Flas

h

Co

n

tro

ll

er

VCORE

ULPD

MISC

I

2

C I/F

I

2

C I/F

DSP SPI

CPORT/

CLIENT

I

2

S

USB

UAR

T

2

JTAG

USIM Interface

Key Bd I/F

LCD/Camera Interface

BT UART

BT

MCSI

MISC

MISC

I

2

C I/F

SPI

BUZ/LPG

PA O/P

PA I/F

FEM

Control

LNA I/P

Memory Control

APC

U200

C13

F15

VEXTH

U13

VMMC

T15

C9

VIO

B15

VEXTL

B17

U10

VPLL

T8

CLK32K

(from U601)

R8

WAKEUP

(to U601)

N10

ONnOFF

(from U601)

T7

CKEN

(from U601)

N8

CKOUT_13MHZ

(to U601)

N9

STARTADC

(to U601)

A16

B16

NC

NC

B14

P8

P1_INT2

(from U601)

1

3

4

2

U637

26MHZ

C221

D15

E15

N7

I

2

C_SCL

R6

I

2

C_SDA

T6

VPLL

VSP_VDR

M8

VSP_VDX

K9

VSP_VFS

R7

VSP_VCK

I

2

S_SCK

P9

T9

I

2

S_SDR

R9

I

2

S_SDX

C246

C245

R214

R223

ND_NWP

M9

I

2

S_WS

L8

(USB_SEO) NC

R5

(USB_DAT) NC

M7

(USB_TXEN) NC

T4

(USB_RCV) NC

A1

AMR_TCK

A2

AMR_TMS

B1

AMR_TDI

B2

AMR_TDO

T1

VIO

T10

R211

(USB_BOOT)

D16

VSI

M

N1

1

US

IM_

R

S

T

T1

1

U

S

IM

_IO

P10

U

S

IM

_C

LK

M1

0

US

IM

_

P

W_

CT

L

U1

1

(V

SS_

PB

IAS)

NC

U2

(SI

M

_

B

IA

S)

N

C

G11..

KB

C(0

:4)

KB

R(0

:4)

NC

L7

U

A

R

T

_R

X

P3

UA

R

T

_

T

X

R2

UA

R

T

_

C

TS

D4

UA

R

T

_

R

TS

C11

D10

K8

DISPLAY_BUSY0

B9

DISPLAY_BUSY1

R4

VIO

N6

VIO

G9

SPI_CLK

F7

SPI_MISO

C5

E6

SPI_MOSI

SPI_NCS0

G17

F17

TXHB

TXLB

E12

G10

M11

TSPACT14

NC (TSPACT15)

APC_OUT

F12

H10

C14

TSPACT11

NC (TSPACT12)

TSPACT13

N17

M17

M16

L16

L17

K17

K16

J16

RXGSMM

RXGSMP

RXEGSMM

RXEGSMP

RXDCSP

RXDCSM

RXPCSP

RXPCSM

E3

L5

NC

(

N

C

S

0)

CS

3

M1

OE

L3

M2

NC

(

N

BHE

)

NC

(

N

BL

E

)

M3

RD

Y

D3

NC

(

ND_CE

1

)

E17

VREF

R15

L1

WE

K6

FD

P

AD

D[2

1

:1

6]

DA

T

A

_

ADD

[0:

15]

G3..

K4..

R1

2

R1

3

N13

C

215

C

216

AD

V

J7

CK

M

L6

C2

GPI

O

_3

4

C4

G7

B3

NC

NC

NC

F5

NC

D2

H7

NC

NC

G5

NC

E1

N15

R16

VREF

T15

J14

F16

VMMC

H17

VDDRF1

K15

D16

Diplexer

2

2

Match/

Filter

Match/

Filter

GSM_OUT

DCS_OUT

4

PA

PA

BiCMOS

Integrated

Power

Amplifier

Controller

Antenna

Switch

Decoder

Match

Match

HBT

SKY77518

U639

11

RF_ANT

RF_PA

6

7

19

17

1

3

2

4

5

VBAT

DC

S_

R

X

GS

M_

RX

GSM_IN

DCS_IN

APC_OUT

(VRAMP)

TSPACT_14

(TX_EN)

TSPACT_13

(BS)

TSPACT_11

(VLOGIC)

1

2

3

4

1

2

3

4

U101

U102

TXLB

TXHB

FL188

4

1

6

7

8

9

RXDCSM

RXDCSP

RXGSMM

RXGSMP

1

2

3

4

5

6

M301

VSIM

USIM_IO_OUT

VSIM

USIM_RST_OUT

USIM_CLK_OUT

R627

USIM_RST

R628

USIM_CLK

R629

USIM_IO

R660

GPIO_34

R345

R344

Q301

R661

(t

o R

344, SI

M

)

(from U200)

USIM_PW_CTL

USIM_IO_OUT

R301

C301

C7 D3 F10 C9

VMEM

C3

RDY

F12....

DATA_ADD(0:15)

D7

VMEM

R318

C5 E3 D12 F5

D4.....

ADD(16:20)

D9

VMEM

R317

C6

D11

E12

C8

D6

D8

FDP

ADV

WE

OE

CKM

CS3

U303

Memory

NC

NC

NC

(selects between GSM/DCS mode)

(controls Rx or Tx mode)

(I/p Supply for DRP2 Analog Cct)

(I/p Supply for DRP2 Analog Cct)

(I/P voltage for DCXO)

(power-on reset signal)

(32Khz Sq wave Signal)

(enable 13MHz clk from the 26MHz xtal)

(Sleep/Wake-up Condition)

(Codec Audio Serial Data O/P)

(frame Sync)

(Codec Audio Serial Data I/P)

(Serial Clock)

Wyszukiwarka

Podobne podstrony:

BD V600 L3 C A3 V1[1] 1

BD C150 L3 C A3 V1[1] 2

BD TripletsR L3 C A3 V1[1] 1

BD Z3 L3 C A3 V1 1

BD V3 L3 C A3 V1[1] 2

BD C200 L3 C A3 v1[1] 0

BD U9 L3 C A3 V1 0

BD K1 L3 C A3 V1 3

BD BlDi V235 L3 C A3 V1[1] 1

Block Diagram W510 L3 C A3 V1 0 Block Diagrams

Block Diagram V3 06 L3 C A3 v1 0

BD W206 W213 A3 C L3 V1

C380 PCB P4c L3 A3 BW V1 0

BL C380 P4c L3 A3 BW V1[1] 0

BL F3 Motofone A3 C L3 A

BL C650 P03 L3 A3 BW V1(1)

BD BlDi E365 A3 C L3 1[1] 2 030611100711

więcej podobnych podstron