094 095

94

xxO xx1

słoń po 921 *toft

impulsie V J An V V blokowonia zablokowanym __*- łtTa inipultu

001

Xt/ 1 5ton P° K*'0) impulsie

przepuszczonym

xx1 xxO

|

M1 |

IM |

M |

m |

W |

W |

m |

JL. | ||

|

oC |

OC |

fi |

fi |

OC |

OC |

8 |

oC |

0 | |

|

p |

OC |

fi |

fi |

OC |

oC |

fi |

fi |

a |

0 |

|

t |

t |

fi |

s |

r |

x |

8 |

8 |

X |

0 |

|

s |

r |

s |

8 |

r |

t |

6 |

8 |

X |

1 |

Rys. 3.36. Graf i tablica przejść/wyjść układu bramkowania generatora z

przykładu 3*14

impulsu zachodzi ac^ = x2 = 1 lub gdy © *2 = 1 i poprzedni impuls był przepuszczony. Działanie projektowanego układu zilustrowane jest na rys. 3.35*

Numerując każdy nowy zestaw x^t ac^ c, y otrzymalibyśmy graf o dwunastu stanach, podlegający minimalizacji. Graf minimalny można jednak uzyskać natychmiast, wyróżniając cztery podstawowe stany układu: blokowanie lub przepuszczanie impulsu, gdy taki się pojawia oraz stan po blokadzie

• -lub po przepuszczeniu w chwilach pomiędzy impulsami. Odpowiedni graf i

tablicę przejść/wyjść przedstawiono na rys. 3*36. U

3.5.2. Struktura układów asynchronicznych

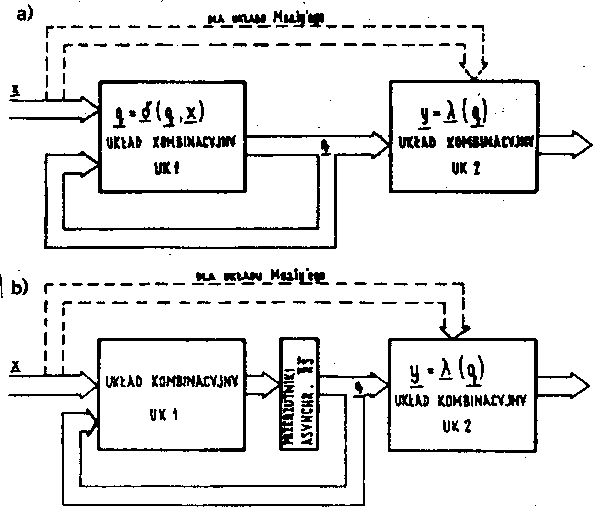

Układ asynchroniczny mole posiadać jedną z dwu struktur przedstawionymi na rys. 3*37«

Rys. 3• 37• Struktury układów asynchronicznych; a) bez przerzutników, b) z asynchronicznymi przerzutnikami RS

W pierwszej z tych struktur układ składa się wyłącznie z układów kombinacyjnych, a rolę układu pamiętającego spełnia układ kombinacyjny UK1 ze sprzężeniem zwrotnym, realizujący funkcję q' = ó(q,x). W drugiej strukturze układ posiada_wyróżnione układy pamiętające."którymi są asynchroniczne przerzutnikl RS.

W układzie asynchronicznym (rys. 3*37) nowy sygnał wejściowy X, wraz z istniejącym stanem q, powoduje pojawienie się na wyjściu UK1 nowego stanu q » w którym układ pozostanie, o ile zachodzi q = ęS(q,x). (Jest to, jak pamiętamy, warunek stabilności przy wejściu x)7 Układ pozostaje w nowym stanie aż do zmiany sygnału wejściowego, który może wywoływać kolejną zmianę stanu itd.

Synteza układu asynchronicznego, gdy posiadamy już zminimalizowany graf będzie polegała na:

Wyszukiwarka

Podobne podstrony:

094 095 2 94 Programowanie liniowe (III) Dla i-0,286 mamy: x, =4,571, x2= 1,143, X

str 094 095 równic przysiadają, chroniąc się za przednią ścianę „SO”. 6. Po wybuch

skanuj0051 94 fMoiMMtWfponMr. (a matematyka jest po prostu narzędziem) ma dość ściśle określone gran

094 095 gu czasowego powinny mieć błędy, zarówno trendów jak i prognoz (prognoz pozornych), niniejsz

094 095 Picea - Pied d alouette - Pieris -- Pin-- Pinus__ Pistia

094 095 Rozdział m np. plany szkoleń, urlopów, terminy zakończenia określonych prac Ud. Organy a, mi

str 094 095 Wróblewskim — życia w nim co prawda było niewiele, ale serce jeszcze wystukiwało rytm.&n

str 094 095 dę rosyjską. Starcie trwało ponad godziną i znowu Callier zarządził odwrót. Walka w tych

str 094 095 Gosiewski odgadł jednak zamiary feldmarszałka Stenbocka. Natychmiast wydał swoim wojskom

str 094 095 Oto okazało się, że Czesi zniszczyli Miechów, zaatakowali też niewielkie miasteczko Żarn

str 094 095 wojskowym uczył” (w dawnym 2 pułku w 1813 roku). Bogusławski, wzruszony do głębi, ze szc

str 094 095 ką przychylność. Wszystkie powstańcze (magazyny wojenne były u włościan. Chłopi służyli

str 094 095 1 rady wojennej zwołane przez wodza na godzinę 7.00 również nie doprowadziły do niczego.

094 095 2. Chcesz wynajęć domek letniskowy. Przyporzędkuj zdania norweskie do polskich

094 tif 94 nych stropów żelbetowych wykonywanych na mokro. Istotnym problemem pozostaje to, aby blac

więcej podobnych podstron