068 069

68

8«Afc

|

N |

«1 |

u |

ia | ||

|

I |

% |

V. |

% |

% | |

|

\ |

* |

y. |

y. | ||

|

n |

•1 |

ti |

n |

1 | |

|

1 |

0 |

1 |

i |

1 |

8 |

|

\ |

1 |

1 |

1 |

1 |

\ |

|

l |

1 |

1 |

i |

1 |

1 |

|

3 |

1 |

1 |

j |

1 |

1 |

i

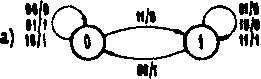

Rys. 3.1. Sumator szeregowy: schemat blokowy oraz grafy i tablice przejść'' /wyjść dla układu Mealy'ego (a) i lfloore'a (b)

Otrzymane grafy mogą być zrealizowane wyłącznie jako układy synchroniczne, bowiem układ asynchroniczny nie jest w stanie rozróżnić kolejnych bitów liczb sumowanych. Ponadto widać, te układ Mealy^ego ma mniejszą ilość stanów niż układ Moore'a. #

Przykład 3.2

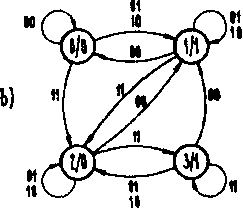

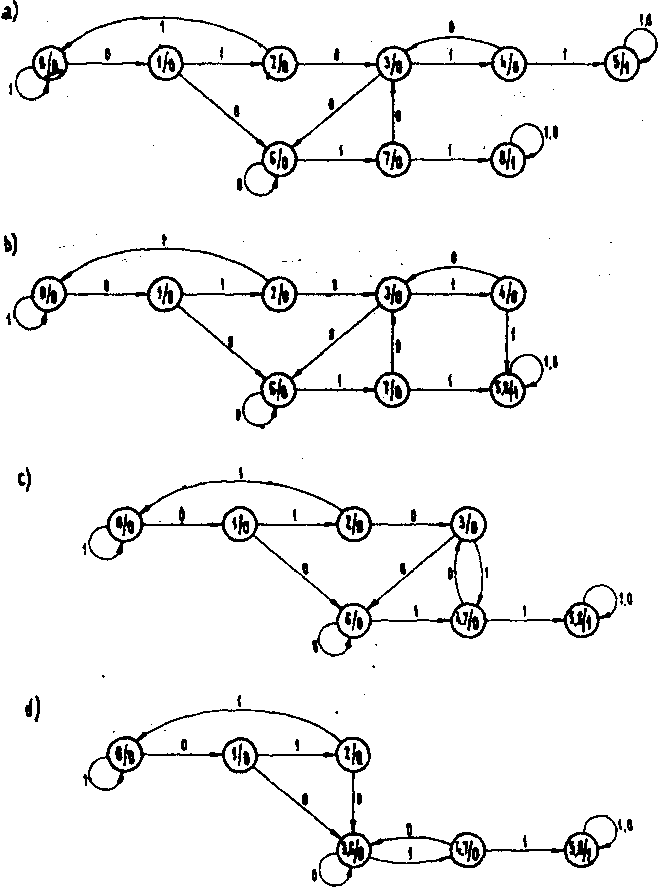

Podać graf układu Moore'a, wykrywającego w ciągu wejściowym sekwencje 01011 lub 0011. Wykrycie jednej z podanych sekwencji ma być zasygnalizowane jedynką na wyjściu, utrzymującą się przez cały dalszy okres działania układu.

Na rys. 3.2a podano graf opisanego układu. Jak widać, niektóre stany w tym grafie są niesprzeczne, t2n. związane są z nimi identyczne wyjścia oraz ze stanów tych, pod wpływem tych samych sygnałów wejściowych, przechodzi się do identycznych nowych stanów.

Niesprzeczne stany można zastąpić jednym, uzyskując w ten sposób graf o mniejszej liczbie stanów. Uproszczenie grafu prowadzi na ogół do uproszczenia układu, a więc jest korzystne.

Na rys. 3.2b,c,d podano kolejne etapy upraszczania grafu. Nowe stany, wprowadzone v; miejsce poprzednich dwóch, oznaczono parą odpowiadających im numerów.

3ys. 3*2. Graf układu z przykładu 3.2a,b,c?d - kolejne etapy eliminacji

zbędnych s5aao:.v

Przykład ten wskazuje, że czasami istnieje możliwość uproszczenia o trzy mane^o pierwotnie grafu. Formalną metodę minimalizacji liczby stand.*, u'-' • du sekwencyjnego podamy w następnym punkcie tego rozdziału.

Wyszukiwarka

Podobne podstrony:

068 069 68 Eliza Mytych. Ludwik Kumański Rys. 3.26. Charakterystyka logarytmiczna fazowa gdzie: k ~

068 069

str 068 069 ZASADY CZĘSC ii I SPOSOBY UŻYCIA

068 069 2 68 Programowanie liniowe Z powyższych warunków wynikają następujące wnioski:Warunek (1-14)

068 069 Wyznaczając prognozy dla jednego momentu prognozowania można wyznaczyć błąd prognoz tylko dl

068 069 Rozdział VI scowych 1 wzmocniła nadzór rządu, realizowany przez starostów, wojewodów oraz mi

str 068 069 kompanie piechoty rozlokowały się wzdłuż rzeki w gęstych zaroślach; kompania Huwalda zaj

str 068 069 sie Mielęcki, odpocząwszy parę chwil, zawezwał Calliera, aby przekazać mu dalsze zleceni

str 068 069 do Prus wchodziła wyłącznie jazda. Były to oddziały litewskie, część koronnych oraz posi

str 068 069 wzgórza, półwysep lub wyspa, bliskość rzeki czy jeziora, miejsce otoczone bagnanji itd.

str 068 069 Napoleon nagle opuścił wyspę Elbę i triumfalnie wrócił do Paryża, skąd w popłochu uciekł

str 068 069 Pod tym widniała pieczęć i podpis .pułkownika Chmieleńskiego. Pismo wypadło z rąk Kality

str 068 069 necki i Milberg poprowadzili przeciwnatarcie, a piechota polska posuwając się z zapałem

068 069 68 Eliza Mytych. Ludwik Kamański Rys. 3.26. Charakterystyka logarytmiczna fazowa gdzie: k ~

068 069 Opis relacji rodzinnych ja, jeg er gift. Nei, jeg er ikke gift. jeg har ingen kjasreste.&nbs

więcej podobnych podstron